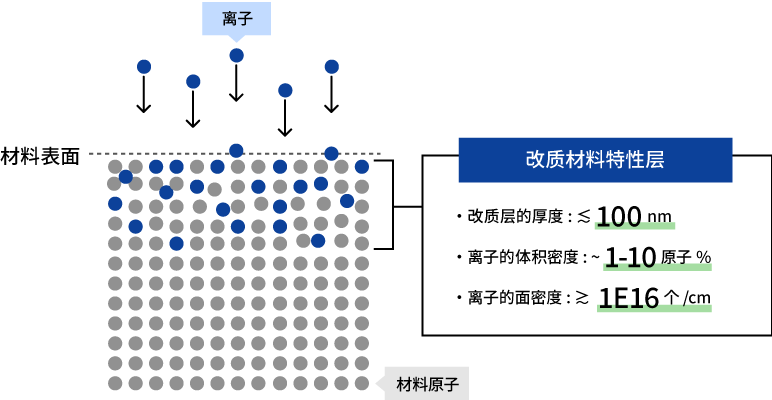

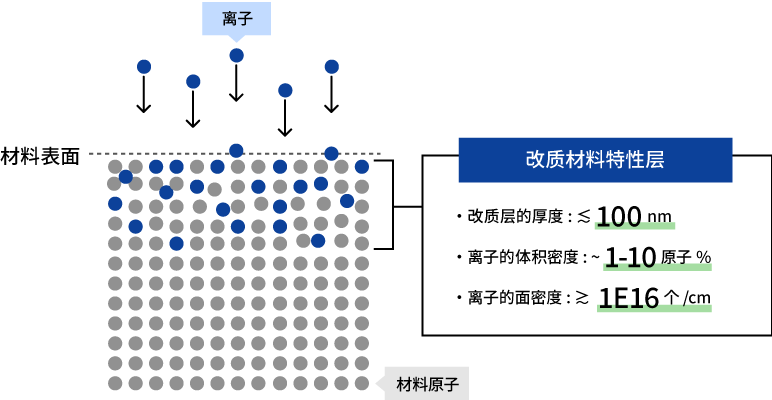

什么是材料改质?

材料改质是通过大量照射离子束来改变材料的特性,从而赋予其新功能或实现以往不可能的加工的一种过程。随着半导体的微细化和复杂化,现有的半导体加工流程在加工精度上出现了局限性,因此这一过程被寄予厚望,期望能在加工技术方面实现突破。

为了发挥材料改质的效果,通常需要向材料表面的浅层区域照射大量离子,以达到大约数原子百分比(atomic%)的浓度,因此需要以低能量进行注入。因此,普通的离子注入装置在生产效率上较低,实用性不足,必须使用专用的材料改质装置才能实现大规模生产。

材料改质的模式图

材料改质的效果

效果及其用途多种多样,已有以下示例被报道。(以下是示例及其相关论文链接)

蚀刻速率的控制

在材料保持不变的情况下,可以改变蚀刻速率。这有助于提高多个材料之间的蚀刻选择比。对于干法和湿法蚀刻均有效。此外,通过改性使得位于表面某一深度的材料不被蚀刻,可以在从表面开始蚀刻时自动停止蚀刻。也就是说,可以形成所需深度的蚀刻停止层。

R. Wada, H. Kai, J. Sasaki, T. Kuroi, T. Ikejiri, “Surface Modification of SiO2 Thin Film using High Dose Ion Implantation Technique as a Manufacturing Worthy Process,” Extended Abstracts of the 2019 International Conference on Solid State Devices and Materials, Nagoya, Japan, 597 (2019).

Y. -S. Chen, T. -W. Chiu, H. -T. Fan, Y. -C. Ko, C. -C. Chen, F. -H. Ko, “Novel Single and Co-Ion Implantation Induced Backside Etch Stop Structures for 3D Multilayer Stacked Package,” 2024 IEEE 74th Electronic Components and Technology Conference (ECTC), Denver, CO, USA, 2184 (2024).

E. Bellandi, V. Soncini, “SiO2 etch rate modification by ion implantation,” Thin Solid Films, 524, 75 (2012).

CMP(chemical mechanical polishing)研磨速率的控制

可以改变研磨速率。这有助于提高异种材料在同一平面上的研磨选择比。此外,通过只改质晶圆的外周部分,还可以使外周的研磨速率降低。这有助于提高晶圆面内的研磨均匀性。

S. Yuan, K. Omori, T. Yamaguchi, T. Ide, S. Muranaka, M. Inoue, “Enhancement of Selectivity for Chemical Mechanical Polishing by Ultra-High-Dose C and Si Ion Implantation,” in IEEE Journal of the Electron Devices Society, 12, 407 (2024).

O. Eryu, K. Abe, N. Takemoto, “Nanostructure formation of SiC using ion implantation and CMP,” Nucl. Instrum. Methods Phys. Res. B, 242, 237 (2006).

掩膜的硬化

可以通过改质掩膜来提高蚀刻耐受性。对有机和无机这两者的掩膜均有效。这使得即使即使比通常薄的掩膜也能进行蚀刻,并抑制光刻胶图案崩坏。此外,因为在蚀刻中掩膜损耗少,所以有助于更精密的深度蚀刻加工。

Takeo Ishibashi, Yoshiharu Ono, Atsumi Yamaguchi, Sachiko Ogawa, Tetsuro Hanawa, Masaaki Shinohara, Masahiro Tadokoro, Kazumasa Yonekura, Yuko Mitani, Keiko Matsuda, Hideaki Hirori, Takashi Miyamoto, Takeshi Matsunobu, “Novel Spin-on Carbon Hard Mask with Hardening by Ion Implantation,” J. Photopolymer Sci. Technol., 20, 365 (2007).

T. Matsumoto, S. Hahto, G. Sacco, H. Kai, R. Wada, T. Kuroi, N. Hamamoto. “High-current metal ion source for material modification in the semiconductor manufacturing processes,” MRS Advances (2025).

区域选择沉积(成膜)

通过对材料表面进行改质,使其钝化,从而在后续的成膜过程中确保该部分不堆积薄膜。如果利用离子束具有指向性特征,可以对具有沟槽图案的基板垂直辐照离子,从而造出仅在沟槽的上部和底部不活化的状态。随后进行成膜时,最终可以获得仅在沟槽侧壁堆积薄膜的结构。

Woo-Hee Kim, Fatemeh Sadat Minaye Hashemi, Adriaan J. M. Mackus, Joseph Singh, Yeongin Kim, Dara Bobb-Semple, Yin Fan, Tobin Kaufman-Osborn, Ludovic Godet, Stacey F. Bent, “A Process for Topographically Selective Deposition on 3D Nanostructures by Ion Implantation,” Nucl. Instrum. ACS Nano 10, 4451 (2016).

M. L. Lee, P. H. Liao, H. Y. Cheng, W. Y. Yen, J. K. Sheu, “UV light-emitting diodes grown on GaN templates with selective-area Si implantation,” Optics Express, 28, 4674 (2020).

应力形成

通过把离子注入材料,就可在材料内部形成应力。利用这一点,可以解决近年来在晶圆上堆积薄膜时逐渐显现的晶圆翘曲问题。当背面形成应力时,则可在不影响表面形成的器件的情况下校正并使晶圆保持平坦。

B. D. Chalifoux, Y. Yao, K. B. Woller, R. K. Heilmann, M. L. Schattenburg, “Compensating film stress in thin silicon substrates using ion implantation,” Optics Express, 27, 11195 (2019).

Lee Wee Teo, Elgin Quek, “Modulation of stress in stress film through ion implantation and its application in stress memorization technique,” United States patent, No. 8119541 (2012).

薄膜剥离

通过在材料表面某一深度的位置局部引入大量的氢离子,可以将该位置作为剥离面,从而仅分离表面层。利用光刻胶图案可以实现局部剥离。此外,在表面粘贴支撑基板后,通过剥离面进行分离,可以获得表面层粘附在支撑基板上的结构。

T. W. Simpson, I. V. Mitchell, G. O. Este, F. R. Shepherd, “Ion implantation induced selective area exfoliation of InP and GaAs,” Nucl. Instrum. Methods. Phys. Res. B, 148, 381 (1999).

H. J. Woo, H. W. Choi, G. D. Kim, W. Hong, J. K. Kim, “Patterned exfoliation of GaAs based on masked helium implantation and subsequent rapid thermal annealing,” AIP Conf. Proc. 1099, 535 (2009).

控制门阈值电压(Vth)

使用金属门形成CMOS的工艺非常复杂。通常需要先制造假门(dummy gate),并在形成源极和漏极,最后去除假门并嵌入金属门。不过,由于pMOS和nMOS使用的门材料不同,因此这一过程需要重复两次。另一方面,如果采用通过改质金属门来改变阈值电压的方法,则可以使用相同的金属材料,同时实现满足pMOS和nMOS两者的阈值电压,从而简化工序。

T. Hayashi, M. Mizutani, M. Inoue, J. Yugami, J. Tsuchimoto, M. Anma, Vth-tunable CMIS platform with high-k gate dielectrics and variability effect for 45nm node, IEEE International Electron Devices Meeting (IEDM) 2005, Washington D.C., 927 (2005).

定向沉积(成膜)

通过大量照射具有指向性的离子束,可以实现定向成膜。对具有沟槽图案的基板进行垂直的离子照射时,薄膜仅会在沟槽的上部和底部堆积,而沟槽的侧壁则不会有薄膜堆积,从而实现了定向成膜。